What is the 3D-Stacked Processor Market Size?

The global 3D-stacked processor market is witnessing rapid growth as semiconductor manufacturers adopt advanced packaging to enhance speed, efficiency, and computing density. The growing demand for high-performance computing and cloud computing is driving the need for cutting-edge 3D stacked processors, fueling market growth. Moreover, the increasing adoption of consumer electronics and automotive electronics is likely to contribute to market growth.

3D-Stacked Processor Market Key Takeaways

- Asia Pacific dominated the global 3D-stacked processor market with the largest share in 2024.

- North America is expected to grow at the fastest CAGR from 2025 to 2034.

- By integration type/stack topology, the 3D-HBM processors (logic + stacked HBM DRAM) segment contributed the largest market share of approximately 35% in 2024.

- By integration type/stack topology, the 3D-heterogeneous integration (CPU + GPU + NPU/TPU/FPGA + memory) segment is expected to grow at approximately 22% CAGR between 2025 and 2034.

- By processor/component type, the AI/ML accelerators / NPUs / TPUs (inference & training accelerators) segment led the market while holding the largest share of approximately 30% in 2024 and is expected to grow at an approximate 25% CAGR between 2025 and 2034.

- By memory integration, the HBM (HBM1/HBM2/HBM2E/HBM3) stacked with logic segment led the market while holding the largest share of approximately 40% in 2024.

- By memory integration, the stacked SRAM on logic segment is expected to grow at a significant CAGR between 2025 and 2034.

- By packaging / interconnect technology, the micro-bump bonding segment led the market while holding the largest share of approximately 45% in 2024.

- By packaging / interconnect technology, the hybrid/direct bonding (oxide/metal hybrid) segment is expected to grow at an approximately 24% CAGR between 2025 and 2034.

- By technology node, the 7 nm and above (legacy/older nodes) segment led the market while holding the largest share of approximately 50% in 2024.

- By technology node, the 3 nm class segment is expected to grow at an approximately 20% CAGR between 2025 and 2034.

- By application, the data centers & cloud servers (HPC, training/inference) segment led the market while holding the largest share of approximately 38% in 2024.

- By application, the edge & telecom (5G base stations, telco edge compute) segment is expected to grow at the highest CAGR between 2025 and 2034.

What is 3D-Stacked Processor Market?

The 3D-stacked market is a rapidly expanding segment within the semiconductor industry, driven by the demand for higher performance, greater energy efficiency, and miniaturization in electronic devices. The market refers to the global industry for processors and system components built using vertical integration, which involves stacking multiple active dies (logic, memory, accelerators, and I/O) and interconnecting them with technologies such as Through- Silicon Vias (TSVs), micro-bumps, hybrid/wafer-bonding, or interposers. 3D stacking delivers significantly higher on-package bandwidth, lower inter-die latency, improved performance-per-watt, and denser form factors compared to planar designs.

Key end-use cases encompass HPC and supercomputing, AI/ML acceleration, data centers, high-end consumer devices such as gaming consoles and mobile SoCs, as well as the automotive and aerospace sectors. Market growth is fueled by rising demand for on-chip memory bandwidth (e.g., HBM), increased AI processing needs, advancements in packaging supply chains, and the push for energy-efficient, high-performance computing solutions.

Key Technological Shift in the 3D-Stacked Processor Market

A key technological shift in the 3D-stacked processor market is the transition from traditional 2.5D packaging to advanced 3D integration using Through-Silicon Vias (TSVs) and hybrid bonding. This evolution enables significantly higher interconnect density, lower latency, and improved energy efficiency by vertically stacking memory and logic components, such as CPUs and high bandwidth memory (HBM), within a single package. Advancements in interconnecting technologies, such as 3D hybrid integration, including through-silicon vias (TSVs), and 3D NAND, are fostering innovations and enhancing market accessibility. The adoption of heterogeneous integration has increased to break down complex system-on-chip (SoC) designs into smaller, more manageable functional blocks. The growing need for high-bandwidth memory (HBM) and investments in packaging infrastructure are driving yield and performance improvements.

- In April 2025, at GTC 2025, NVIDIA unveiled two CPO-based networking switch platforms: Spectrum-X Photonics for Ethernet (launching 2026) and Quantum-X Photonics for InfiniBand (late 2025). Spectrum-X offers up to 2,048 ports at 200 Gb/s, achieving a bandwidth of 400 Tb/s, while Quantum-X supports 144 ports at 800 Gb/s using 200 Gb/s SerDes. Both platforms feature the world's first 3D-stacked silicon photonics engine, utilizing TSMC's 3D hybrid bonding technology, which was developed in collaboration with partners such as Coherent, Lumentum, Corning, Foxconn, and ASE. These innovations aim to boost bandwidth and energy efficiency for AI-driven data centers. (Source: https://www.idtechex.com )

3D-Stacked Processor Market Outlook

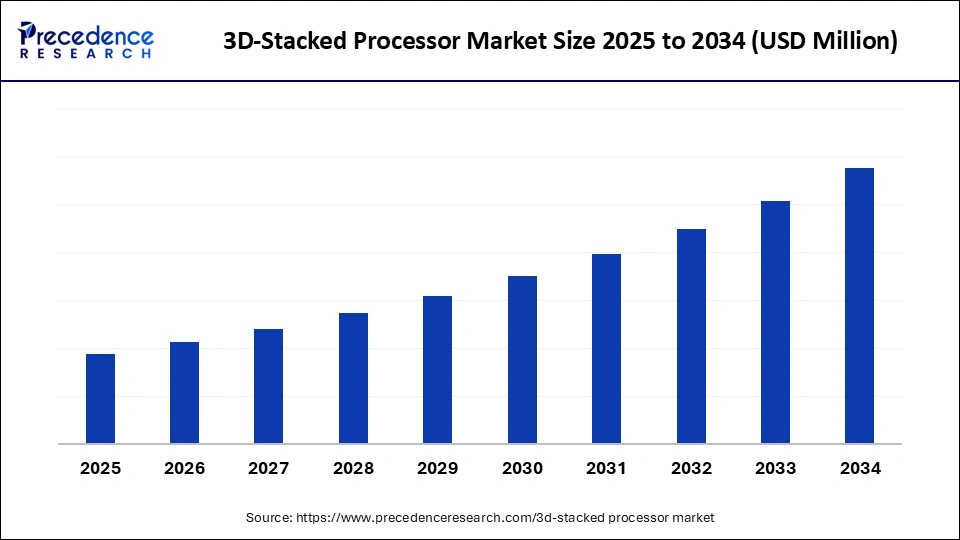

- Industry Growth Overview: The 3D-stacked processor industry is expected to experience significant growth between 2025 and 2034 due to increased consumer demand for high-performance computing, energy-efficient semiconductors, and integration of AI and ML. The growing demand for faster data processing and the emphasis on advancements in semiconductor technology are driving the industry's growth.

- Global Expansion: The 3D-sctaked processor industry is expanding rapidly in regions like Asia Pacific, North America, and Europe with increased investments & funding for the semiconductor sector. The expansion of burgeoning consumer electronics , rapid industrialization, and the existence of leading semiconductor manufacturers in emerging countries are fueling this growth.

- Major Investors: Private industry investors and strategic investors like TSMC (Taiwan Semiconductor Manufacturing Company), Intel Corporation, Samsung Electronics, and SK Hynix are driving innovations and developments in 3D-stacked processors. Micro Technology, Advanced Micro Devices (AMD), NVIDIA, and ASE Technology Holdings are also major investors in the 3D-stacked processor technology.

Market Scope

| Report Coverage | Details |

| Dominating Region | Asia Pacific |

| Fastest Growing Region | North America |

| Base Year | 2024 |

| Forecast Period | 2025 to 2034 |

| Segments Covered | Integration Type / Stack Topology, Processor / Component Type, Memory Integration, Packaging / Interconnect Technology, Technology Node, Application, and Region |

| Regions Covered | North America, Europe, Asia-Pacific, Latin America, and Middle East & Africa |

Market Dynamics

Drivers

Increased Demand for High-performance Applications

The increasing demand for cutting-edge computational power, adoption of AI and ML technologies, and expansion of cloud-based HPC solutions are driving the growth of the 3D-stacked processor market. The use of AI and ML is leading to an increasing need for 3D-stacked processors due to the increasing complexity of these applications. The high-performance computing solutions offer dense integration of logic and memory. The rapid utilization of electronics and the need for faster data processing in data centers and the high-performance computing ecosystem are driving the adoption of 3D-stacked processor technologies.

Restraint

High Cost

3D-stacked processors require specialized equipment and materials, which contribute to the high cost. The complex fabrication process, including through-silicon via (TSV) formation and sustaining initial investments required for research & development, testing, and design of compact 3D structure, further adds to the expenses. Working with 3D-stacked processors needs specialized expertise and skills, which lead to higher labor costs and a longer development cycle. The frequent infrastructure upgrades in 3D stacked processors further increase the overall cost, making it inaccessible for small and medium-sized organizations.

Opportunity

Technological Advancements

Technological advancements, such as through-silicon via (TSV) technology, 3D hybrid bonding, monolithic 3D integration, heterogeneous integration, and advanced packaging technologies, are holding significant growth opportunities for the market. These technologies are enabling direct-to-direct interfaces and reducing interconnect resistance. The ability to enhance signal integrity, reduce power consumption, and enhance overall performance makes it ideal for 3D-stacked processors. The innovations in 3D-stacked processor technology are gaining traction due to the adoption of advanced technologies like HPC (high-performance computing), AI, ML, and IoT, which increases the demand for 3D stacked processors.

Segment Insights

Integration Type/Stack Topology Insights

How Does the 3D-HBM Processors Segment Dominate the 3D-Stacked Processor Market?

The 3D-HBM processors (logic + stacked HBM DRAM) segment dominated the market with a 35% share in 2024. This is mainly due to their high bandwidth memory and lower power consumption. The 3D-HBM processors, including both logic and stacked HBM DRAM, are essential for high-performance computing applications such as AI, ML, and data analytics . The 3D-HBM processors play a vital role in enhancing performance, throughput, and handling data-intensive workloads, as well as advancing next-generation system architectures for technologies such as cutting-edge graphics, cloud computing, and AI.

The 3D-heterogeneous integration (CPU + GPU + NPU/TPU/FPGA + memory) segment is expected to expand at the highest CAGR of approximately 22% over the forecast period. This is mainly due to its key role in enhancing performance and reducing latency. Advancements in semiconductor technologies, such as through-silicon vias (TSVs) and hybrid bonding, are driving the adoption of 3D-heterogeneous integration for more efficient and compact designs. These integrations, such as CPU, GPU, NPU, TPU, and FPGA, enable efficient energy and performance through specialized hardware, reduce data transfer latency, and offer smaller form factors.

Processor/Component Type Insights

Which Component Type Lead the 3D-Stacked Processor Market in 2024?

The AI/ML accelerators / NPUs / TPUs (inference & training accelerators) segment led the market with a 30% share in 2024 and is expected to grow with an approximate 25% CAGR over the forecast period. This is mainly due to their high usage in increasing processing power and density. The increased utilization of 3D-stacked processors, driven by increased need for power efficiency, specialized architectures, and higher performance, is contributing to this segment's growth. AI/ML accelerators, NPUs, and TPUs enable high memory bandwidth, capacity, and advanced AI capabilities.

Memory Integration Insights

Why Did the HBM Stacked with Logic Segment Dominate the Market in 2024?

The HBM (HBM1/HBM2/HBM2E/HBM3) stacked with logic segment dominated the 3D-stacked processor market with a 40% share in 2024. This is primarily due to its ability to offer higher bandwidth and lower latency. The HBM is stacked with logic providing greater capacity and power efficiency. This memory integration enables smaller form factors, rather than conventional memory, allowing for the overcoming of bottlenecks in higher-performance applications, such as HPC and AI.

The stacked SRAM on logic segment is expected to expand at the fastest CAGR in the upcoming period, driven by its ability to enhance density and reduce footprint. The integration of stacked SRAM logic enables higher performance and enhances energy efficiency. This memory integration addresses the memory wall through challenges such as thermal dissipation, high upfront costs for 3D packaging technology, and complex integration.

Packaging/Interconnected Technology Insights

What Made Micro-Bump Bonding the Dominant Segment in the Market in 2024?

The micro-bump bonding segment dominated the 3D-stacked processor market while holding about 45% share in 2024 due to its capability to support 3D integration. This technology creates dense interconnections between stacked dies, thereby reducing signal lengths to support higher speeds and lower power consumption. Advancements in technologies, such as finer microbumps and alternative methods like hybrid bonding, are playing a crucial role in scaling performance in AI, data centers, and HPC applications through the use of microbumps.

The hybrid/direct bonding (oxide/metal hybrid) segment is expected to expand at a 24% CAGR during the projection period, owing to its ability to increase interconnect density. The need for development of ultra-fine pitch interconnects enables high-density and high-bandwidth chips integration, driving adoption of hybrid/direct bonding (oxide/metal hybrid) technology. This technology offers superior electrical performance and improves reliability compared to traditional methods.

Technology Node Insights

Which Technology Node Segment Dominate the 3D-Stacked Processor Market?

The 7 nm and above (legacy/older nodes) segment dominated the market with a 50% share in 2024 due to its affordability and advancements. The 7 nm and above (legacy/older nodes) technology nodes are cost-effective in manufacturing. The demand for high-performance computing has increased, driving a shift toward technology nodes of 7 nm and above in applications such as AI, ML, and data centers.

The 3 nm class segment is likely to grow at the fastest CAGR of 20% between 2025 and 2034. This is due to its high use in increasing transistor density. The 3 nm class enables high performance, transistor density in smaller footprints, and reduces power consumption. This technology node enables the creation of cutting-edge chips and integrated circuits for sophisticated, compact, and energy-efficient electronic devices.

Application Insights

Why Did the Data Centers & Cloud Servers Segment Dominate the Market in 2024?

The data centers & cloud servers (HPC, training/inference) segment dominated the 3D-stacked processor market with approximately 38% share in 2024. This is mainly due to increased demand for high-performance computing (HPC) in data centers and cloud servers. The need for comprehensive training and inference in cloud services drives the adoption of 3D-stacked processors, enabling high-density, high-performance, and power-efficient architectures. The increased need for these processors in data centers & cloud servers enables high investments in higher memory bandwidth and increased transistor density.

The edge & telecom (5G base stations, telco edge compute) segment is expected to grow at the fastest CAGR over the forecast period due to the increased need for low-latency processing in edge & telecom applications. The significant growth in 5G infrastructure and telco edge computing requires capable processors for handling intense computation and data processing at the edge of the network. The 3D-stacked processor enables real-time application support and high-performance for edge & telecom technologies.

Regional Insights

What Made Asia Pacific the Dominant Region in the 3D-Stacked Processor Market?

Asia Pacific dominated the global 3D-stacked processor market by holding the largest share in 2024 due to its robust semiconductor manufacturing ecosystem. The region benefits from a confluence of world-leading foundries, extensive supply chains, and formidable R&D clusters, which give it a unique strategic edge. There is a heightened demand for semiconductors amplified by the proliferation of smartphones, high-performance computing, and AI-driven consumer electronics, which collectively require unprecedented computational efficiency. The uniqueness of 5G adoption has further elevated the appetite for processors with high bandwidth and compact architecture. The market growth in Asia Pacific is also sustained by its vast, youthful, and technologically voracious consumer base.

China is a major contributor to the market. The country has become both a leading manufacturer and a major consumer of 3D-stacked processors. National strategies to reduce dependency on foreign technologies are channeling unprecedented investment into local fabs and research hubs. With its colossal demand from AI, data centers, and consumer electronics, China maintains a strong market presence in the Asia Pacific.

What Makes North America the Fastest-Growing Market for 3D-Stacked Processors?

North America is the fastest-growing region in the global market. High demand for AI, cloud hyperscale, and defense-grade computing solutions supports its growth trajectory. Its technological ecosystem thrives on symbiosis between academia, research institutions, and private enterprises, leading to breakthroughs in advanced packaging and heterogeneous integration. Venture capitalists in the region continue to invest substantial capital in startups that promise innovative designs, ensuring the area remains a hub of innovation. Furthermore, the burgeoning EV industry has amplified processor demand for autonomous systems, driving the market growth.

Country-Level Investments & Funding for 3D-Stacked Processor Industry

- U.S.: U.S. leveraging the CHIPS and Science Act, enabling funding for cutting-edge packaging, R&D, and domestic manufacturing capabilities, including 3D stacking technologies.

- Canada: In June 2025, Canada accelerated its semiconductor industry with the FABrIC announcement of a total investment of $35.6 million, up from $13.4 million in funding for market-ready innovations.

- China: In 2014, China launched its chip fund with three planned phases spanning 25 years, and launched $48 billion for phase three in May 2024.

- South Korea: The Government proposed the Yongin semiconductor cluster back in 2019, following through with subsidies and regulatory assistance. The government also announced $19 billion in funding in May 2024.

- India: The new semiconductor projects under the India Semiconductor Mission, approved by the Union Cabinet. These projects involve an investment of Rs 4,600 crore in India's first commercial compound fabrication facilities.

3D-Stacked Processor Market Value Chain Analysis

- Raw Material Procurement (Silicon Wafers, Gases)

The 3D-stacked processors require high-quality materials in manufacturing to advance integrated circuits (IC) with techniques that need additional specialized materials, including silicon, metals, and dopants.

Key Players: Samsung Electronics, Intel, SK Hynix, and Amkor Technology.

- Testing and Quality Control

Testing & quality control of 3D-stacked processors is a multi-stage process, with the primary goal of ensuring known-good dies (KGD) before stacking.

Key Players: Siemens, Intel, and TSMC.

- Distribution to OEMs and Integrators

Distribution of 3D-sctaked processors to OEMs and integrators is a complex and highly specialized process. The distribution models for these processors depend on direct relationships and collaboration with several key market players, like foundries and cutting-edge packaging houses.

Key Players: Intel, Samsung Electronics, Amkor, ASF, and GlobalFoundries.

Top Companies in the 3D-Stacked Processor Market & Their Offering:

- Taiwan Semiconductor Manufacturing Company (TSMC): TSMC is the world's largest semiconductor foundry, offering cutting-edge 3D packaging solutions, including InFO and CoWoS.

- Samsung Electronics: It utilizes its own 3D stacking technologies to stack memory and logic on dies vertically.

- Intel Corporation: has emphasized the development of its own 3D stacking advancements, particularly in the field of Embedded Multi-die Interconnect Bridge (EMIB) technology, resulting in smaller and more powerful processor creations.

- NVIDIA Corporation: It offers cutting-edge processors for AI and high-performance computing. NVIDIA is a major customer for TSMC's cutting-edge 3D stacking technologies, such as CoWoS-L, for integrating multiple logic and memory dies.

- Micron Technology: offers 3D NAND technologies that stack memory cells vertically on a chip, enabling higher densities and improved performance in processors.

3D-Stacked Processor Market Companies

- Advanced Micro Devices (AMD) / Xilinx

- SK hynix

- Broadcom

- Applied Materials

- ASE Technology / ASE Group

- Amkor Technology

- Qualcomm

- Apple Inc.

- IBM Research / IBM Systems

- TSMC ecosystem partners

Recent Developments

- In April 2025, SK Hynix Inc., the world's top DRAM memory chipmaker, launched its 3D HBM as the next game-changer in the AI chip race. This memory chip is designed for revolutionizing AI memory with reduced latency and higher efficiency. (Source: https://www.kedglobal.com )

- In March 2025, AMD introduced its Ryzen 9 9950X3D and 9900X3D processors at CES 2025. The 9950X3D has 16 cores, 32 threads, and 144MB of cache, and the 9900X3D has 12 cores, 24 Threads, and 140MB of cache.

Exclusive Expert Analysis on the 3D-Stacked Processor Market

The 3D-stacked processor market is poised at a strategic inflection point, driven by exponential compute demands across AI/ML workloads, hyperscale data centers, and high-performance edge deployments. The confluence of maturing advanced packaging ecosystems, particularly 3D integration techniques such as TSVs, hybrid bonding, and chiplet architectures, has catalyzed a paradigm shift in system-level performance scaling beyond the constraints of traditional Moore's Law.

Structurally, the market is transitioning from early adoption to accelerated deployment, underpinned by robust tailwinds: the proliferation of AI accelerators requiring high-bandwidth, low-latency interconnects; a growing reliance on HBM-integrated SoCs; and a global pivot toward energy-optimized compute infrastructure. Notably, vertical integration strategies by leading semiconductor players and sovereign technology ambitions, especially in Asia-Pacific, signal a long runway for capital investment and IP monetization.

From a risk-adjusted opportunity lens, 3D-stacked architectures unlock differentiated value across multiple verticals, including autonomous systems, defense-grade aerospace compute, and next-gen consumer electronics. With ecosystem convergence among foundries, OSATs, EDA vendors, and optical interconnect innovators, the market represents a compelling growth vector for stakeholders positioned to leverage co-packaged optics, silicon photonics, and heterogeneous integration at scale.

Segment Covered in the Report

By Integration Type / Stack Topology

- 3D-SoC (Logic + memory + I/O vertically stacked)

- 3D-HBM Processors (Logic + stacked HBM DRAM)

- 3D-Heterogeneous Integration (CPU + GPU + NPU/TPU/FPGA + memory)

- 3D-NAND + Compute (storage + compute co-integration)

- 2.5D + 3D Hybrid (interposer + stacked dies)

- Monolithic 3D (future/advanced wafer-level monolithic stacking)

By Processor / Component Type

- CPUs (general-purpose processors using 3D integration)

- GPUs (graphics/compute with stacked memory)

- AI/ML Accelerators / NPUs / TPUs (inference & training accelerators)

- FPGAs & Reconfigurable ICs (stacked logic + memory)

- ASICs & Custom Accelerators (domain-specific chips)

- Memory Stacks (HBM, stacked SRAM, 3D-NAND modules)

By Memory Integration

- HBM (HBM1/HBM2/HBM2E/HBM3) stacked with logic

- Stacked SRAM on logic

- 3D-NAND co-packaged with logic/storage controllers

- Hybrid memory-logic configurations (e.g., logic+on-die cache layers)

By Packaging / Interconnect Technology

- Through-Silicon Vias (TSVs)

- Micro-bump bonding

- Hybrid/Direct Bonding (oxide/metal hybrid)

- Wafer-to-Wafer bonding

- Die-to-Wafer bonding

- Interposer (silicon or organic) based 2.5D/3D hybrids

By Technology Node

- 7 nm and above (legacy/older nodes)

- 5 nm class

- 3 nm class

- Sub-3 nm / advanced nodes (future roadmap)

By Application

- Data Centers & Cloud Servers (HPC, training/inference)

- Artificial Intelligence & Machine Learning workloads

- High-Performance Computing (Supercomputers)

- Consumer Electronics (high-end mobile, gaming consoles, AR/VR)

- Automotive (autonomous driving SoCs, ADAS compute)

- Edge & Telecom (5G base stations, telco edge compute)

- Aerospace, Defense & Industrial Automation

By Region

- North America

- Europe

- Asia-Pacific

- Latin America

- Middle East & Africa

For inquiries regarding discounts, bulk purchases, or customization requests, please contact us at sales@precedenceresearch.com

Frequently Asked Questions

Ask For Sample

No cookie-cutter, only authentic analysis – take the 1st step to become a Precedence Research client

Get a Sample

Get a Sample

Table Of Content

Table Of Content

sales@precedenceresearch.com

sales@precedenceresearch.com

+1 804-441-9344

+1 804-441-9344

Schedule a Meeting

Schedule a Meeting