What is the Data Center AI Chip Packaging Market Size?

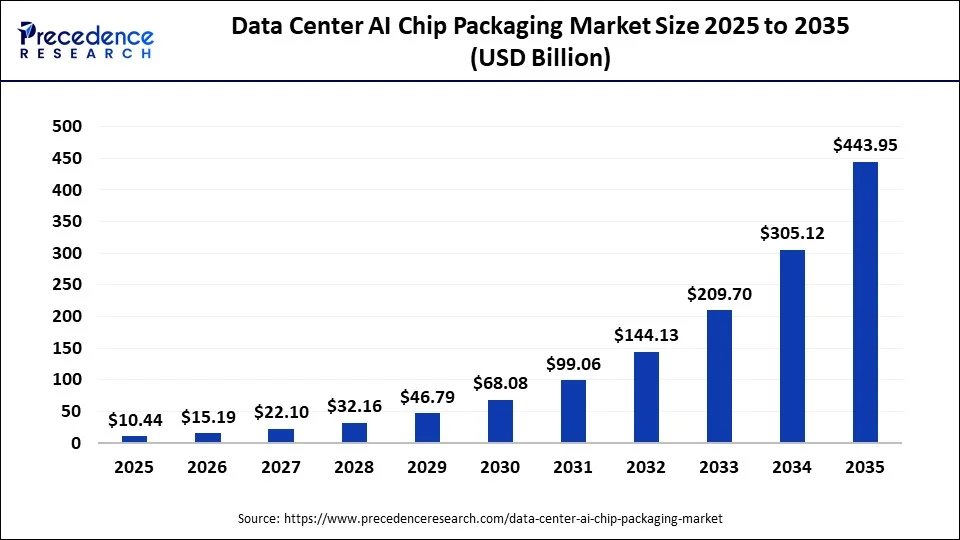

The global data center AI chip packaging market size accounted for USD 10.44 billion in 2025 and is predicted to increase from USD 15.19 billion in 2026 to approximately USD 443.95 billion by 2035, expanding at a CAGR of 45.50% from 2026 to 2035. The market is growing significantly due to the large-scale adoption of AI technology across major sectors, necessitating AI data centers with advanced chip packaging to reduce power consumption and meet the explosive global demand for AI chips.

Market Highlights

- North America accounted for the largest market share in 2025.

- Asia Pacific is expected to grow at the fastest CAGR between 2026 and 2035.

- By packaging type, the flip-chip packaging segment held the largest market share in 2025.

- By packaging type, the wafer-level packaging segment is projected to grow at the fastest CAGR between 2026 and 2035.

- By material type, the copper pillar & solder bump materials segment contributed the largest market share in 2025.

- By material type, the advanced thermal & low-K materials segment is poised to grow at a strong CAGR between 2026 and 2035.

- By application, the AI training accelerators segment captured the biggest market share in 2025.

- By application, the generative AI & large model accelerators segment is projected to grow at the fastest CAGR between 2026 and 2035.

Data Center AI Chip Packaging with Innovation Unlocked

The data center AI chip packaging market focuses on advanced assembly and integration technologies developed specifically for semiconductors to enable AI workloads in data centers . The market is experiencing a major shift due to the explosive growth of LLMs and the growing demand for generative AI , driven by improved efficiency and system-level scaling. AI chip packaging is the process of enclosing semiconductor chips, called dies, and connecting them to a circuit board. Traditional methods fall short for AI chip packaging, prompting the adoption of advanced packaging techniques such as 2.5D/3D integration. It offers multiple chiplets combining high-bandwidth memory within a single package to minimize data bottlenecks.

Data Center AI Chip Packaging Market Outlook

- Industry Growth Overview: The market is largely expanding due to the increasing AI arms race among leading tech giants, growing demand for faster data handling in real-time, and ongoing advancement in packaging technologies such as 3D integration, aiming to offer extended chip performance beyond conventional scaling of transistors.

- Sustainability Trends: The market is witnessing various sustainability trends, including liquid cooling for energy-efficient processes, AI optimization, renewable energy integration, and water conservation. Companies are leveraging AI to optimize data center operations, such as dynamic workload balancing. Also, the use of recycled and refurbished hardware has seen a surge in demand, as consumers recognize the value of a circular economy and reduce e-waste.

- Major Investors: The market is propelled by the convergence of major investors, private equity, and venture capital funding, along with strategic investments and collaborations between emerging startups and key market players. Leading companies like TSMC, Intel, and AMD are increasingly investing roughly $165 billion in new packaging and fabrication facilities across Europe and the U.S., supported by government incentives such as the U.S. CHIPS Act.

Market Scope

| Report Coverage | Details |

| Market Size in 2025 | USD 10.44 Billion |

| Market Size in 2026 | USD 15.19 Billion |

| Market Size by 2035 | USD 443.95 Billion |

| Market Growth Rate from 2026 to 2035 | CAGR of 45.50% |

| Dominating Region | North America |

| Fastest Growing Region | Asia Pacific |

| Base Year | 2025 |

| Forecast Period | 2026 to 2035 |

| Segments Covered | Packaging Type, Material Type, Application, and Region |

| Regions Covered | North America, Europe, Asia-Pacific, Latin America, and Middle East & Africa |

Segmental Insights

Packaging Type Insights

Why Is Flip-Chip Packaging Type Preferred in the Data Center AI Chip Packaging Market?

The flip chip packaging segment held the largest market share in 2025. The segment is dominating as it offers excellent electrical performance, maximized input and output density, and better thermal management, which are critical factors for the high-power AI workload requirements. The flip-chip design significantly reduces inductance, resistance, and parasitic capacitance, which is highly beneficial for enhancing signal integrity and enabling faster transmission.

The wafer-level packaging segment is projected to grow at the fastest CAGR during the forecast period. The segment is hugely growing as this packaging provides a significant reduction in package size and weight/height, which in turn facilitates compact electronic devices. This minimization enables lighter, more portable electronic devices without affecting their functionality.

Material Type Insights

What Are the Benefits of the Copper Pillar & Solder Bump Materials in the Data Center AI Chip Packaging Market?

The copper pillar & solder bump materials segment held the largest market share in 2025. The segment is dominating because it offers superior benefits, such as high-density interconnect capability, better thermal and electrical performance, and improved mechanical stability. Copper pillar enables finer pitch and higher I/O density, which are highly required for advanced silicon nodes and compact AI processors. Also, superior resistance to electromigration makes it more reliable for high-current AI applications.

The advanced thermal & low-k materials segment is projected to grow at the fastest CAGR during the foreseeable period. The segment is growing rapidly due to benefits such as efficient heat dissipation, which reduces performance degradation and the risk of failure in high-power AI chips, thereby further enhancing computational throughput.

Application Insights

Why Are AI Training Accelerators Founds Extensive Applications in the Data Center AI Chip Packaging Market?

The AI training accelerators segment held the largest market share in 2025. The segment is dominating due to the extreme computational demands, especially for LLMs and deep learning processes that require massive amounts of data processing and complex computations, necessitating specialized hardware. AI training accelerators are heavily dependent on advanced chip packaging to meet the growing demand for modern AI, thereby strengthening the application of advanced packaging.

The generative AI & large model accelerators segment is projected to grow at the fastest CAGR during the foreseeable period. The segment is growing as the massive computational demands of generative AI and large model accelerators require highly specialized, energy-efficient hardware solutions. This is achievable by advanced packaging technologies.

Regional Insights

What Made North America a Dominant Region in the Data Center AI Chip Packaging Market?

North America held the largest market share in 2025, supported by the strong concentration of global technology leaders with deep capabilities in semiconductor design, advanced packaging, and software development. Companies headquartered or operating at scale in the region lead the design of high-performance processors, accelerators, and custom silicon optimized for AI and machine-learning workloads. The exponential growth in AI model training, inference deployment, and interface-intensive applications has increased demand for compact, power-efficient chips capable of supporting hyperscale data centers . These facilities require advanced packaging solutions that reduce latency, improve thermal management, and enable higher compute density while controlling energy consumption.

Tech-savvy enterprises across cloud computing , financial services, healthcare analytics, and autonomous systems further accelerate demand for advanced AI chip packaging to improve performance-per-watt and overall cost efficiency. Government support plays a reinforcing role in sustaining regional leadership. The United States CHIPS and Science Act provides direct incentives for domestic semiconductor manufacturing, research, and advanced packaging development, including funding for pilot lines and workforce training. These programs encourage investments in technologies such as chiplet-based architectures, heterogeneous integration, and advanced interconnects.

North America leads in chiplet integration through packaging approaches such as 2.5D and 3D integration, silicon interposers, and advanced substrate technologies, which enable high-bandwidth memory access and improved power efficiency. This combination of strong private-sector innovation and targeted public investment continues to position North America at the forefront of advanced AI chip packaging and semiconductor system integration.

U.S. Data Center AI Chip Packaging Market Trends

The market is experiencing rapid growth as semiconductor manufacturers and system designers accelerate the shift toward advanced packaging architectures such as 2.5D and 3D integration to overcome the physical and performance limits of traditional scaling. These packaging approaches enable higher interconnect density, shorter signal paths, and improved bandwidth between logic and memory components, which are essential for compute-intensive AI workloads. In the United States, this transition is closely tied to efforts to strengthen domestic supply-chain resilience and reduce dependence on offshore manufacturing for critical semiconductor technologies.

Government incentives play a central role in this expansion. Programs under the U.S. CHIPS and Science Act support domestic investment in advanced semiconductor manufacturing , packaging research, and pilot production lines, with specific emphasis on heterogeneous integration and advanced interconnect technologies. U.S.-based players are actively deploying system-level packaging approaches such as chiplet architectures, silicon interposers, and through silicon vias to enable scalable performance gains without relying on further transistor miniaturization. Technologies such as Intel's EMIB and Foveros platforms exemplify this approach by allowing multiple dies to be tightly integrated into a single package with high bandwidth and improved power efficiency.

How Is the Asia Pacific Data Center AI Chip Packaging Market Rapidly Expanding?

Asia Pacific is projected to grow at the fastest CAGR during the foreseeable period, driven by the region's strategic push to position itself as a global hub for advanced semiconductor manufacturing, electronics equipment, and next-generation packaging innovation. Governments across Taiwan, South Korea, Japan, China, and Singapore continue to prioritize semiconductor self-sufficiency and high-value manufacturing through sustained investment in fabrication, advanced packaging facilities, and workforce development. These efforts directly support the rapid adoption of 2.5D and 3D integration technologies required for AI accelerators, high-performance computing, and data center processors.

Leading semiconductor players are central to this growth trajectory. Taiwan Semiconductor Manufacturing Company has significantly expanded its advanced packaging capacity through platforms such as CoWoS and InFO to support the integration of high-bandwidth memory for AI processors.

Intel has increased investment in advanced packaging and assembly operations across Asia, including Malaysia, to scale technologies such as chiplet-based integration and heterogeneous packaging needed for AI and cloud workloads. Regional foundries and outsourced semiconductor assembly and test providers are also upgrading substrate technologies, interconnect density, and thermal management solutions to meet higher computational and power efficiency requirements. The combination of strong government backing, manufacturing scale, and rapid adoption of AI-driven workloads positions Asia Pacific as the fastest-growing region in advanced chip packaging.

China Data Center AI Chip Packaging Market Analysis

China is a leading contributor to the expansion of the Asia-Pacific data center AI chip packaging market, driven by sustained investment in advanced chip packaging technologies to strengthen domestic semiconductor capacity. Chinese semiconductor firms and research institutes are prioritizing advanced packaging approaches, such as chip-on-wafer-on-substrate technologies, high-density interposers, and advanced substrate engineering, to support AI accelerators and application-specific integrated circuits for data centers. These packaging solutions are critical for enabling high-bandwidth memory integration, improved thermal performance, and compact form factors required for large-scale AI training and inference workloads.

Geopolitical pressure and export control constraints have further accelerated China's focus on semiconductor self-reliance, making advanced chip packaging a strategic priority rather than a downstream manufacturing step. National and provincial funding programs support investments in outsourced assembly and testing facilities, advanced packaging pilot lines, and domestic substrate supply chains.

What Are the Driving Factors of the European Data Center AI Chip Packaging Market Growth?

Europe's expansion in the data center AI chip packaging sector is primarily driven by rapidly rising demand for AI workloads and high-performance computing, as well as a strong regional focus on power efficiency and sustainability. European data centers supporting AI training, inference, and scientific computing increasingly require packaging solutions that deliver higher bandwidth, lower latency, and reduced energy consumption per operation. This has accelerated adoption of advanced packaging approaches that enable performance gains without relying solely on further transistor scaling.

Technological innovation plays a central role in this growth. European semiconductor and research ecosystems are actively advancing heterogeneous integration, three-dimensional stacking, and chiplet-based architectures to overcome the physical and economic limits associated with traditional Moore's law scaling. These packaging techniques enable multiple dies with distinct functions, such as logic, memory, and I/O, to be integrated into a single system with optimized power delivery and thermal management. Such designs are especially important for AI accelerators deployed in energy-constrained data center environments, where efficiency directly impacts operating costs and carbon targets.

UK Data Center AI Chip Packaging Market Trends

The market is largely driven by sustained large-scale investment in artificial intelligence , rapid expansion of cloud computing infrastructure, and targeted government spending aimed at strengthening independence across the semiconductor value chain. In the United Kingdom, this momentum is reinforced by national priorities to advance sovereign capabilities in chip design, advanced computing, and optoelectronics , rather than relying exclusively on offshore manufacturing. Growth in hyperscale and enterprise data centers supporting AI model training, inference, and analytics is directly increasing demand for advanced AI chip packaging solutions that improve power efficiency, bandwidth, and system-level performance.

The UK's strong position in AI research and deployment further amplifies this demand. Government-backed initiatives such as the UK National AI Strategy and continued funding through UK Research and Innovation support the development of advanced computing, photonics, and semiconductor design capabilities. The country has a deep concentration of AI-driven enterprises, research institutions, and design-focused semiconductor firms that specialize in system architecture, interconnects, and energy-efficient compute. As AI workloads scale across financial services, healthcare, life sciences , and climate modeling, packaging technologies that enable high-density integration, efficient thermal management, and chiplet-based architectures become critical.

How Is the Middle East and Africa Data Center AI Chip Packaging Market Fueling Notably?

The region is expanding due to global tech giants such as Microsoft, Google Cloud, and AWS, along with regional players that are heavily investing in large-scale and hyperscale data center construction, mainly across the Gulf countries and South Africa, to handle data-intensive AI workloads. The Middle East and Africa region has abundant resources and substantial capital from sovereign wealth funds, further propelling its growth in the data center and AI chip packaging markets.

UAE Data Center AI Chip Packaging Market Analysis

The UAE is investing billions of dollars to expand AI infrastructure, aiming to offer AI services globally, along with significant chip procurement, including GPUs from Nvidia. The region's abundant oil, gas, and solar power further provides a continuous and reliable energy supply for AI data centers, a critical factor for other regions.

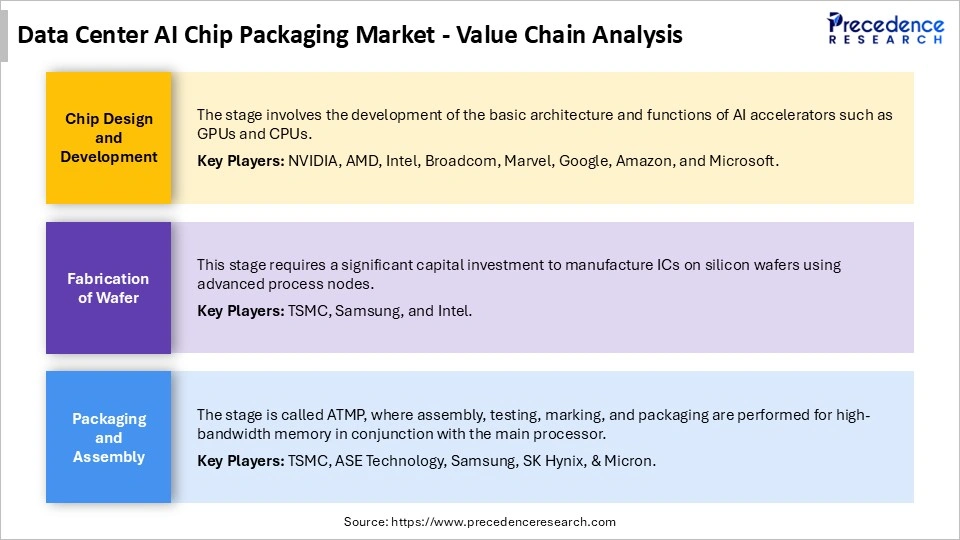

Data Center AI Chip Packaging Market Value Chain

Top Companies in Data Center AI Chip Packaging Market & their Offerings

- NVIDIA

- Taiwan Semiconductor Manufacturing Company

- Advanced Micro Devices (AMD)

- Intel Corporation

- Samsung Electronics

- Amazon Web Services

- Microsoft

- Meta Platforms

- Broadcom

- Marvell Technology

- ASE Technology Holding

- Amkor Technology

- Powertech Technology Inc.

- Tongfu Microelectronics Co., Ltd.

Recent Developments

- In June 2025, the latest Research performed by Cleantech Groups shows that innovative methods for advanced chip packaging are transforming the semiconductor market by offering huge energy savings, higher performance, and substantially minimizing production costs.(Source: https://cleantech.com )

- In October 2025, a new report presented by Bloomberg Intelligence shows that the advanced semiconductor packaging market will be projected to grow eightfold to $80.5 billion by 2033, owing to the larger adoption of AI chips from data centers into consumer electronics and automotive applications.(Source: https://www.bloomberg.com )

Segments Covered in the Report

By Packaging Type

- Flip-Chip Packaging

- Wire-bond packaging

- Wafer-level packaging

- Advanced Packaging (2.5D & 3D IC)

By Material Type

- Copper Pillar & Solder Bump Materials

- Epoxy Molding Compounds

- Underfill Materials

- Advanced Thermal & Low-K Materials

By Application

- AI Training Accelerators

- AI inference accelerators

- Networking & switching chips

- Generative AI & Large-Model Accelerators

By Region

- North America

- Europe

- Asia-Pacific

- Latin America

- Middle East and Africa

For inquiries regarding discounts, bulk purchases, or customization requests, please contact us at [email protected]

Frequently Asked Questions

Ask For Sample

No cookie-cutter, only authentic analysis – take the 1st step to become a Precedence Research client

Get a Sample

Get a Sample

Table Of Content

Table Of Content

+1 804-441-9344

+1 804-441-9344

Schedule a Meeting

Schedule a Meeting